2025年3月12日 記

はじめに

CPUのスペックを確認しようとあちこちのホームページを見て回っていると、

CPUのキャッシュメモリについても当然書いてあるのですが、よく「2次キャッシュと3次キャッシュで合計〇〇MB」という感じの変な記述を見かけます。

今まであまり気にしていなかったのですが、

最近ちょっと気になってしまったのでキャッシュメモリについて私が知っていることを、

CPUのマニュアルを踏まえて記しておこうと思い立ちました。

一応お断りしておきますが、もしかしたら本記事中に誤った記述が含まれているかもしれません。

意図的に誤った記述をするつもりはありませんが、もし気になるところがありましたらご容赦ください。

目次

(1)キャッシュメモリとは

(2)CPU(コア)とキャッシュメモリ、3次キャッシュ、メインメモリの構成

(3)最後に

(1)キャッシュメモリとは

CPUの動作速度が25MHzを超えてきたあたりからだったと思いますが、

CPUには「キャッシュメモリ」というものが内臓されるようになったと思います。

x86 CPUだとi486(80486)からだったと思います。

インテルのx86に対してモトローラのMC68000シリーズがアップルのMacintoshに搭載されていましたが、

こちらはMC68020には既に命令キャッシュが搭載されていました。

いや、もっと言えばMC68010というCPUには「ループモード」と呼ばれるものが付いていて、

比較的簡単な分岐命令専用のキャッシュだったようです。

どうでもいい話かもしれませんが、i486を搭載したパソコンが出た当時、

起動時に表示されるメモリチェック機能のメモリアクセス速度がえらい速くて「本当にメモリにアクセスしているのか!?」と思った記憶があります。

更についでにどうでもいい話ですが、

モトローラのMC68000シリーズですがMC68040以降は動作速度を上げることができずに廃(すた)れてしまった感じでした。

内部(レジスタ構成とか)が比較的綺麗に作られていたのですが、

それが仇(あだ)となってしまったようでした。

16bitと言われていたMC68000 CPUですが16MBのメモリ空間を自由にアクセスできたため、大きくて複雑なプログラムを作るには向いていたと思います。

対してx86 CPUは64KBの「セグメント」というもので区切られてしまっていたため、

16bitのアドレスレジスタと4bitシフトした16bitのセグメントレジスタを組み合わせておよそ1MBのメモリ空間にアクセスできましたが、

「セグメント」で区切られてしまっていたために64KBを超えた巨大データにアクセスする際にはすごく面倒な手順を踏む必要がありました。

パソコンを使うだけの人からすればそんなことはプログラマが苦労してくれれば良かっただけでしょうが、

プログラミングをやっていた(私も含めた)当事者からすれば本当に「気が狂いそう」になるくらい酷(ひど)い仕様でした。

そんなこともあって当時、私はインテルのCPUを搭載したパソコンを使うのが嫌でモトローラのCPUを搭載していたパソコンを使っていました。

CPUの動作クロックが上がってくると、

メインメモリへのアクセス速度がボトルネックとなって思ったほどの処理速度の向上が見られなくなったのだと思います。

高速で動作するCPUの処理速度を落とさないようにするため、CPUには「キャッシュメモリ」と呼ばれるものが搭載されるようになりました。

プログラムやデータは、ある瞬間瞬間で見ますと比較的小さな範囲を繰り返し使っていることが多くて、

その小さな範囲をCPU内部に記憶しておくことで、ある程度処理速度の低下を防ぐことができます。

そんなわけで高速CPUにはプログラム(命令やデータ)を記憶しておくための「キャッシュメモリ」というものが搭載されるようになりました。

(2)CPU(コア)とキャッシュメモリ、3次キャッシュ、メインメモリの構成

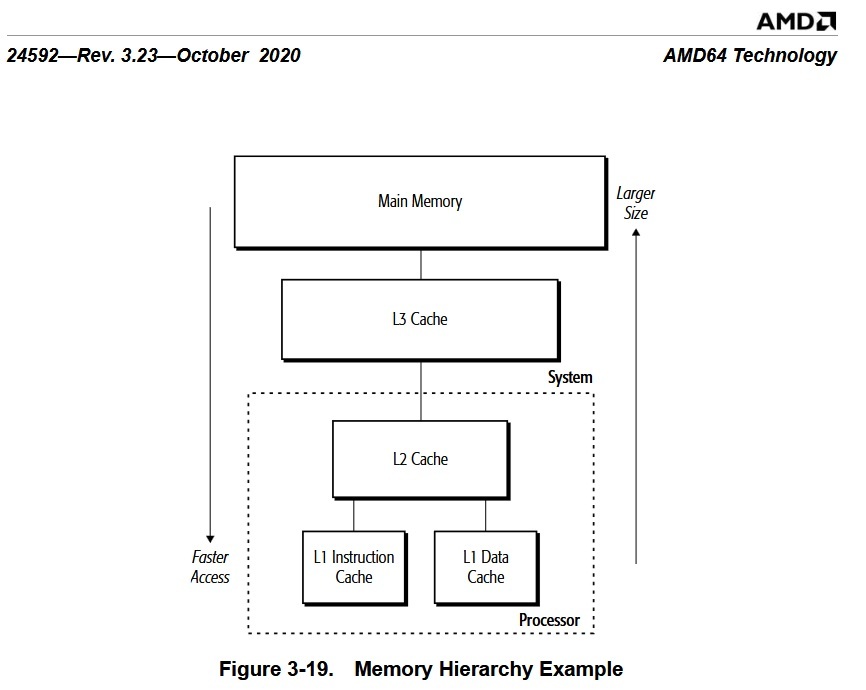

まずは下図をご覧ください。

下図はAMDの【AMD64 Architecture Programmer's Manual】というマニュアルの一部を抜粋させて頂いたものです。

図のProcessorとして点線で囲まれている部分はCPU(コア)の内部で、

1次キャッシュはInstruction(命令)キャッシュとData(データ)キャッシュに分かれていて、

それぞれが2次キャッシュに接続されています。

1次キャッシュは「ハーバードアーキテクチャー」と呼ばれる命令とデータが分離されているキャッシュ構成です。

どこかで「ハーバードアーキテクチャー」という言葉を聞いたことはありませんか?

命令キャッシュとデータキャッシュが分離されていることで得られる利点は2つあります。

ひとつは、CPU(コア)が命令キャッシュとデータキャッシュを別々に、

そして同時にアクセスできるため通常のメモリアクセスと比較して単純に倍速でアクセスできるようなイメージになります。

当然ですが1次キャッシュはCPU(コア)と同じ速度で動作していますので、

1次キャッシュにヒットする限りCPU(コア)は速度を落とすことなく最速で動作可能になっています。

もうひとつは、命令キャッシュとデータキャッシュが分離されているためにキャッシュにヒットしないような巨大なデータにアクセスする際には、

少なくとも命令キャッシュだけは巨大なデータに食いつぶされることなくヒットし続けることができますので、無駄に処理速度の低下を招くことはありません。

当然ですがデータキャッシュのほうは巨大なデータに食いつぶされてしまいますので、処理速度の低下を招いてしまいます。

そしてその1次キャッシュは(図では)その上の2次キャッシュに接続されています。

2次キャッシュもCPU(コア)に含まれていますが、1次キャッシュに比べると動作速度は遅い(はず)です。

その代わりに2次キャッシュは1次キャッシュに比べると大容量になっています。

2次キャッシュは1次キャッシュと違って命令とデータの混合キャッシュになりますので、

巨大なデータにアクセスする際には、その巨大なデータにすべて食いつぶされる可能性があります。

ただし「おそらく」なのですが、

無駄にキャッシュが食いつぶされることを防ぐためにキャッシュ制御命令とかがCPUの命令セットに用意されていると思いますので、

(どの程度制御できるかを私は知りませんし、知るつもりも今のところありませんが)ある程度はコントロールできるのだろう・・・と思っています。

ちょっと余談ですが、「なぜ1次キャッシュと2次キャッシュに分かれているのか?」という疑問を持たれるかもしれません。

同じメモリなら全部1次キャッシュにしてしまえばよいのに・・・とね。

今現在の事情として、どうなっているのかを私は知りませんが昔の話をしますと、

昔は高速なメモリというのはとても高価で大容量を実装するのは金銭的にも、

また無駄に大きな容量のキャッシュメモリを搭載してもヒット率が必ず(劇的に)向上するというものでもありませんでした。

そんなわけで高速で高価な1次キャッシュは大容量を搭載するわけには行きませんでした。

「高価」という意味では、「1次キャッシュは2次キャッシュよりも動作が複雑である」とも言い換えることができると思います。

同じ「メモリ」という言葉で表現されていますが、

少なくともSSDとかUSBメモリとかと同一のモノでは無くて、高速で複雑な制御を伴うモノとお考えいただければ良いと思います。

2次キャッシュは(図では)その上の3次キャッシュに接続されています。

3次キャッシュはCPU(コア)の外に配置されているのでCPU(コア)から見るとメインメモリと同じような扱いになっているようです。

購入する際にはCPUのスペックを確認すると思いますが、CPUのスペックには3次キャッシュも当然含まれています。

しかしAMD64アーキテクチャーには3次キャッシュについての具体的な記述は無いようです。

その代わり、関連するプロトコルとかの定義とかはあるようですので、

3次キャッシュはCPUごとに自由に設計できるようになっているようです。

・・・逆にそうしないとコア数とかがAMD64アーキテクチャーで固定されてしまうことになり、

コア数と価格の自由な設定ができなくなってしまいますよね

・・・というのが(今のところ)私の推測です。

マニュアルをちゃんと読んで確認したわけではありませんのでご注意くださいね。

CPU(コア)本来の機能と3次キャッシュは分離されているものであって、

AMD64のマニュアルをちょっと見てみた程度なので詳細は不明ですが、

この3次キャッシュというものは1次キャッシュや2次キャッシュと違ってコア間通信とかの役割も担っているのではないかと思われます。

コア間通信機能が無いとマルチコアとして機能させられませんので、

3次キャッシュを利用してその辺の処理も行っているのではないかと思います。

AMD64のマニュアルの3次キャッシュの説明の中に下記のような記述がありました。

L3 Cache Range Reservation.

The L3 Cache Range Reservation feature allows a portion of the L3 cache to be reserved for a specific system physical address range. This capability is intended to reduce access latency for a specified.

(翻訳ソフトによる日本語訳)

L3 キャッシュ範囲の予約。

L3 キャッシュ範囲予約機能を使用すると、L3 キャッシュの一部を特定のシステム物理アドレス範囲用に予約できます。 この機能は、指定したアクセス待ち時間を短縮することを目的としています。

この説明から、3次キャッシュは「プログラムよりメインメモリ(物理メモリ)の特定の部分を指定してキャッシュすることも可能」なようです。 1次キャッシュや2次キャッシュのように機械的にキャッシュするものとは異なるものであることが分かります。

(3)最後に

以上、私が知っている範囲内でAMD64のマニュアルの内容も一部含めて記しました。 少し「誤解」などが含まれていたとしても、 あなたがCPUの「キャッシュメモリ」について理解を深められたとしたらそれでよいと思っています。 正確な情報が欲しいのであれば頑張ってCPUのマニュアルと格闘して(読んで)くださいね。